Katedra Mikroelektroniki i Technik Informatycznych Politechniki Lódzkiej; Komputerowe projektowanie ukladów

+JS=1E-16

TOX=3.5E-8

NSUB=6.9E15

+XJ=0.6E-6

LD=0.47E-6

+UO=255

UCRIT=5.8E4 UEXP=0.42

Uwaga: do symulacji ukladów CMOS należy zastosować następujące opcje (w Multisim nie jest to

konieczne):

.OPTIONS DEFL=20U DEFW=16.5U DEFAD=60P DEFAS=60P

.OPTIONS VNTOL=20M ABSTOL=20P RELTOL=0.01 NOMOD NOPAGE

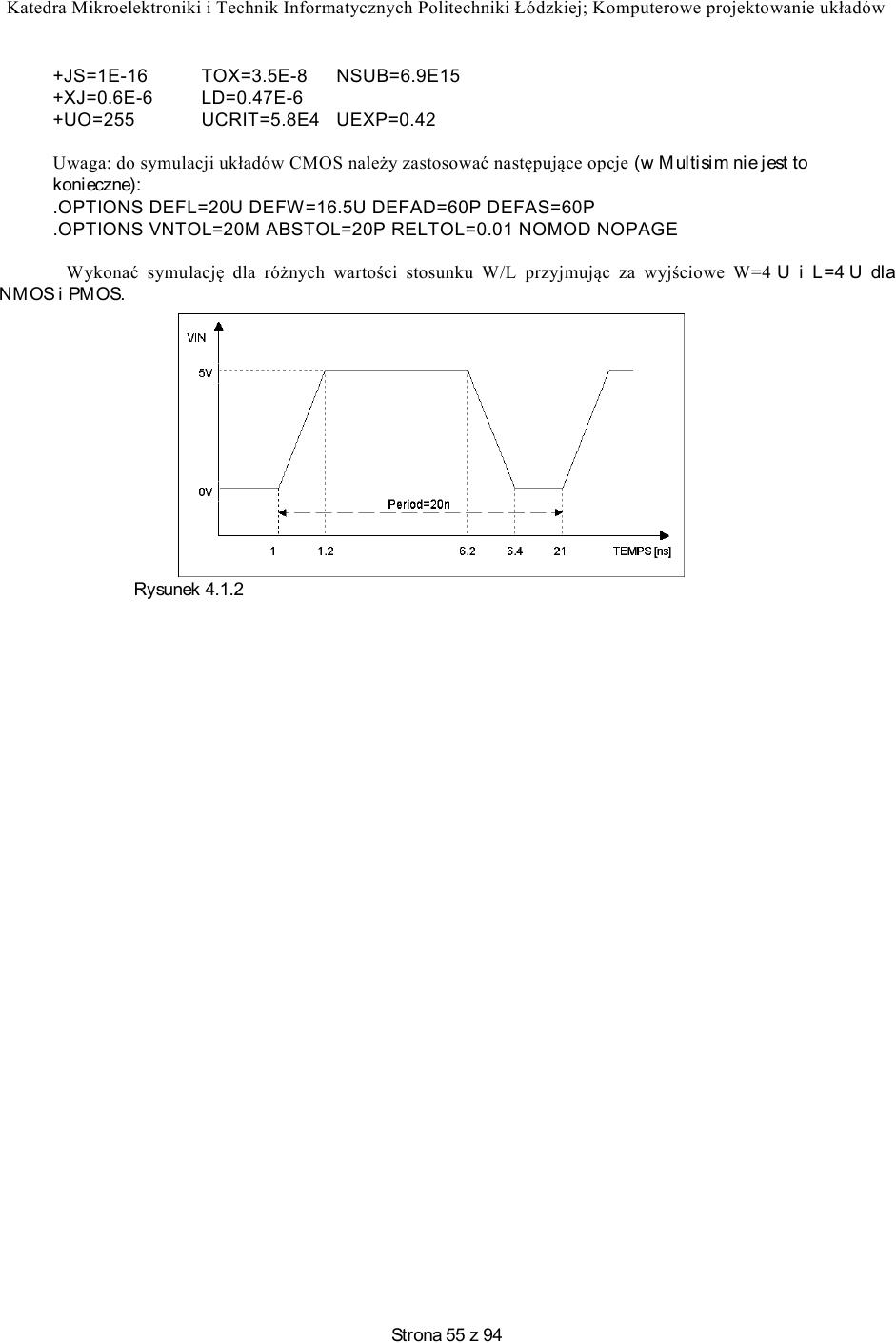

Wykonać symulację dla różnych wartości stosunku W/L przyjmując za wyjściowe W=4 U i L=4 U dla

NMOS i PMOS.

Rysunek 4.1.2

Strona 55 z 94