Katedra Mikroelektroniki i Technik Informatycznych Politechniki Lódzkiej; Komputerowe projektowanie ukladów

Ćwiczenie 4 (Tydzień 14, opcja 1) Uklady CMOS

Zadanie 4.1 (Tydzień 14, opcja 1.1) Symulacja inwertera wykonanego w

technologii CMOS

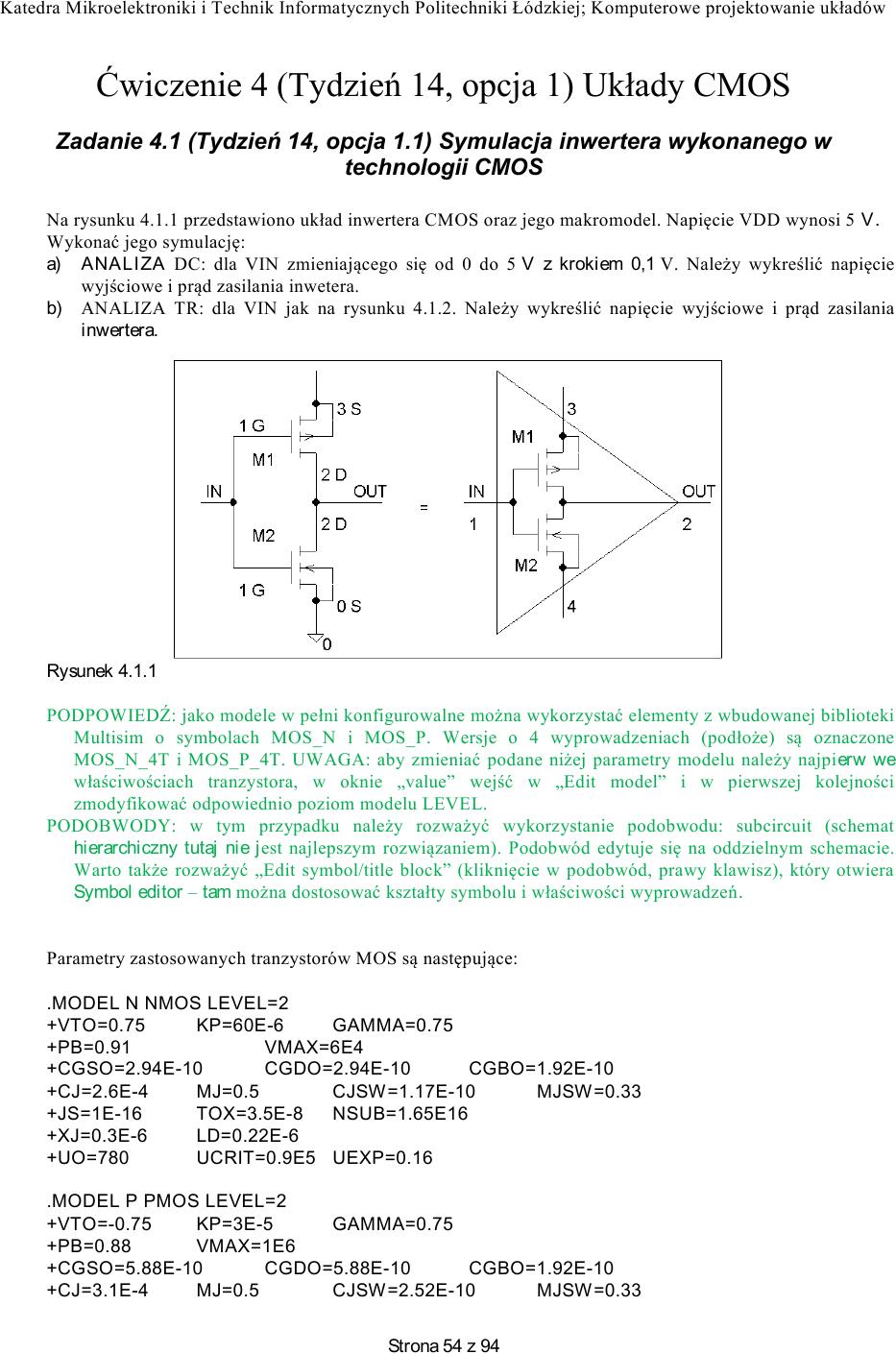

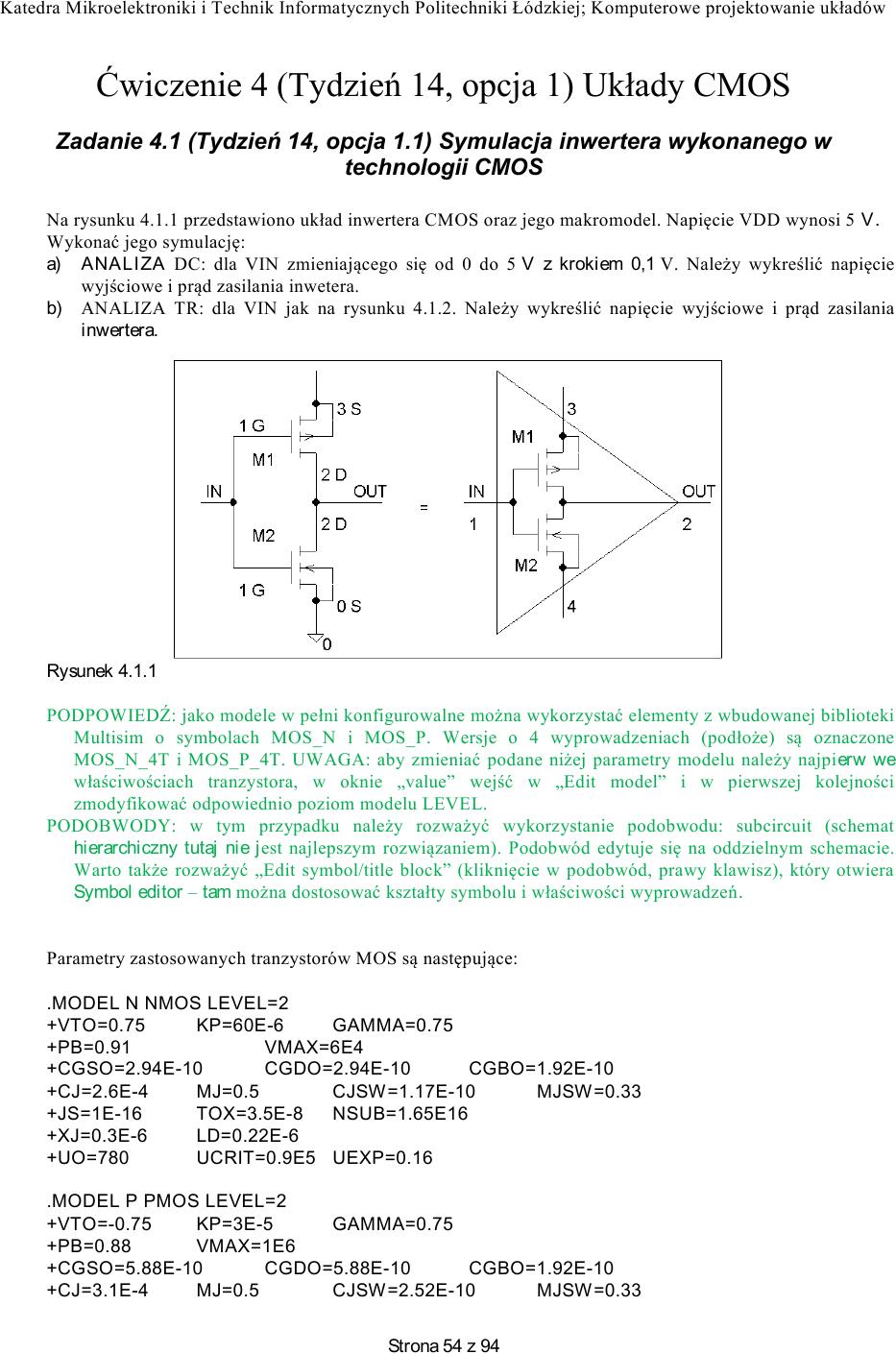

Na rysunku 4.1.1 przedstawiono uklad inwertera CMOS oraz jego makromodel. Napięcie VDD wynosi 5 V.

Wykonać jego symulację:

a) ANALIZA DC: dla VIN zmieniającego się od 0 do 5 V z krokiem 0,1 V. Należy wykreślić napięcie

wyjściowe i prąd zasilania inwetera.

b) ANALIZA TR: dla VIN jak na rysunku 4.1.2. Należy wykreślić napięcie wyjściowe i prąd zasilania

inwertera.

Rysunek 4.1.1

PODPOWIEDŹ: jako modele w pelni konfigurowalne można wykorzystać elementy z wbudowanej biblioteki

Multisim o symbolach MOS_N i MOS_P. Wersje o 4 wyprowadzeniach (podloże) są oznaczone

MOS_N_4T i MOS_P_4T. UWAGA: aby zmieniać podane niżej parametry modelu należy najpierw we

wlaściwościach tranzystora, w oknie ,,value" wejść w ,,Edit model" i w pierwszej kolejności

zmodyfikować odpowiednio poziom modelu LEVEL.

PODOBWODY: w tym przypadku należy rozważyć wykorzystanie podobwodu: subcircuit (schemat

hierarchiczny tutaj nie jest najlepszym rozwiązaniem). Podobwód edytuje się na oddzielnym schemacie.

Warto także rozważyć ,,Edit symbol/title block" (kliknięcie w podobwód, prawy klawisz), który otwiera

Symbol editor tam można dostosować ksztalty symbolu i wlaściwości wyprowadzeń.

Parametry zastosowanych tranzystorów MOS są następujące:

.MODEL N NMOS LEVEL=2

+VTO=0.75

KP=60E-6

GAMMA=0.75

+PB=0.91

VMAX=6E4

+CGSO=2.94E-10

CGDO=2.94E-10

CGBO=1.92E-10

+CJ=2.6E-4

MJ=0.5

CJSW =1.17E-10

MJSW =0.33

+JS=1E-16

TOX=3.5E-8

NSUB=1.65E16

+XJ=0.3E-6

LD=0.22E-6

+UO=780

UCRIT=0.9E5 UEXP=0.16

.MODEL P PMOS LEVEL=2

+VTO=-0.75

KP=3E-5

GAMMA=0.75

+PB=0.88

VMAX=1E6

+CGSO=5.88E-10

CGDO=5.88E-10

CGBO=1.92E-10

+CJ=3.1E-4

MJ=0.5

CJSW =2.52E-10

MJSW =0.33

Strona 54 z 94